# Monolithic Pixel Sensors for Future Collider Experiments

C. Marinas

IFIC – Valencia

#### Introduction

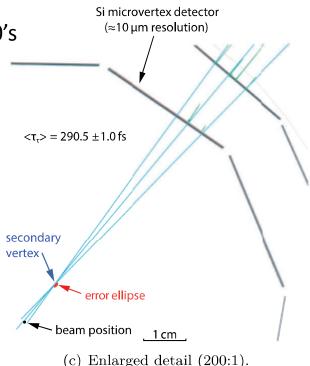

Semiconductor detectors have been used for energy measurements since the 1960's

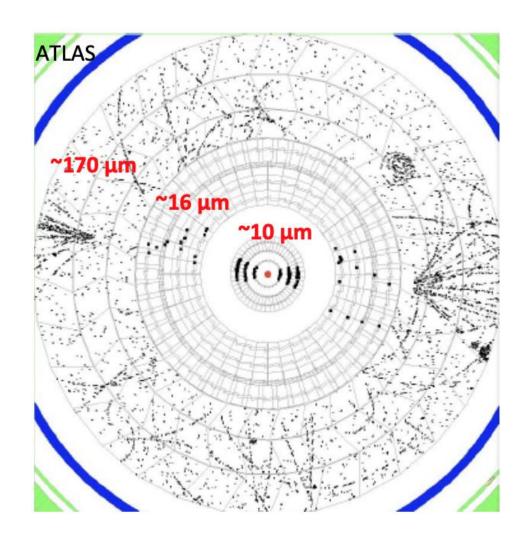

• In the 1980's, the availability of microfabrication technology, with the possibility of structuring the electrodes at the 50-100  $\mu$ m level has vastly improved the position resolution, down to 10  $\mu$ m or below.

- → Secondary vertices from short-lived particles (tau, B, D) become accessible

- It has radically changed the way experiments are thought of and conducted

- Today, virtually every high energy physics experiment deploys semiconductor detectors

Fig. 8.1 Event display of the reaction  $e^+e^- \to Z^0 \to \tau^+\tau^-$  in which one of the two  $\tau$  leptons decays into three pions. Panels (b) and (c) show enlarged details demonstrating the precise measurement of track hits in the silicon microvertex detector and the recognition of a so-called 'secondary vertex' (OPAL detector at the  $e^+e^-$  collider LEP, source: CERN).

## Nowadays: Silicon Everywhere

### Tasks of Tracking Detectors

- Provide precise space points or space point clusters (vectors) originating from ionizing charged particles

- Particle track finding from patterns of measured hits

- Momentum (B-field) and angle measurement

- Measurement of primary and secondary vertices

- Multi-track separation and vertexing in the core of (boosted) jets

- Measurement of the specific ionization (dE/dx)

- Keep the material influencing the paths of the particles to a minimum to avoid scattering in the material and secondary interactions

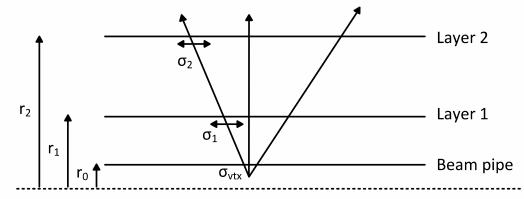

### **Vertex Resolution**

Concentrating here on properties for vertexing in HEP experiments

Vertex resolution

$$\sigma_{vtx} = \sqrt{\frac{r_1}{r_2 - r_1}} + 1 \int_{0}^{2} \sigma^2 + (2r_1 - r_0)^2 (13.6 \,\text{MeV})^2 \frac{x}{X_0} \frac{1}{p^2}$$

#### **Detector requirements**

- Fine segmentation

- Low material (beam pipe and detector layers)

- First layer as close as possible to the beam pipe

- Large lever arm

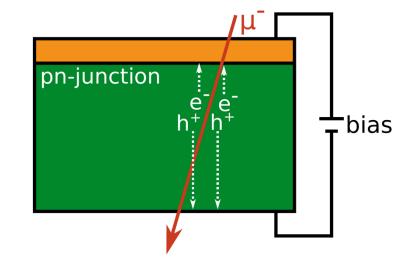

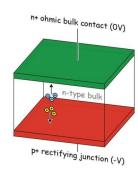

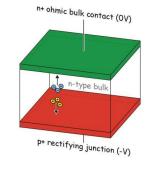

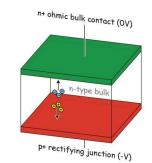

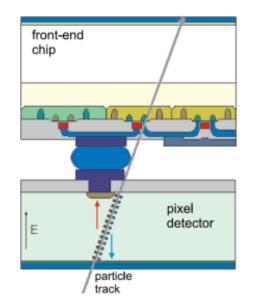

#### Silicon Detectors

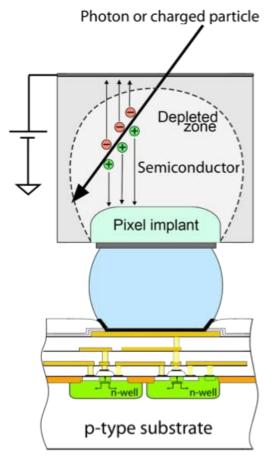

- Particles flying through the bulk produce ionization

- Ionization creates charges in the detector volume:

- Electron-hole pairs in a semiconductor detector

- Electric field applied to move the charges and 'induce' an electric current

- Simplest detector: pn-junction

- Operated in reverse bias → Depletion region

- Traversing particle → Ionization = signal carriers in the silicon

- Typical thickness 50 300 μm

- Shockley-Ramo Theorem:

Moving charges induce signal on electrode

## Increasing the Resolution: Segmentation

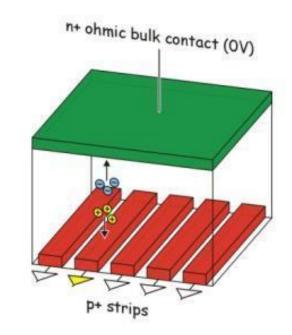

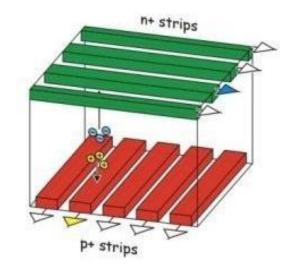

#### Silicon strip detectors

A strip detector is an arrangement of strip like shaped implants acting as charge collecting electrodes (one-dimensional array of diodes).

Double sided silicon strip detectors

Two dimensional position measurements can be achieved by applying an additional strip like doping on the wafer backside by use of a double sided technology.

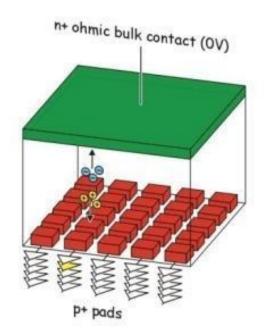

Pixel detectors

2D array of pixels. Each pixel = 1 pn-junction True 2 dimensional information without ambiguities

## Increasing the Resolution: Segmentation

• Silicon strip detectors

A strip detector is an arrangement of strip like shaped implants acting as charge collecting electrodes (one-dimensional array of diodes).

Two dimensional position measurements can be achieved by applying an additional strip like doping on the wafer backside by use of a double sided technology.

Pixel detectors

2D array of pixels. Each pixel = 1 pn-junction True 2 dimensional information without ambiguities

## Increasing the Resolution: Segmentation

• Silicon strip detectors

A strip detector is an arrangement of strip like shaped implants acting as charge collecting electrodes (one-dimensional array of diodes).

Two dimensional position measurements can be achieved by applying an additional strip like doping on the wafer backside by use of a double sided technology.

#### Pixel detectors

2D array of pixels. Each pixel = 1 pn-junction True 2 dimensional information without ambiguities

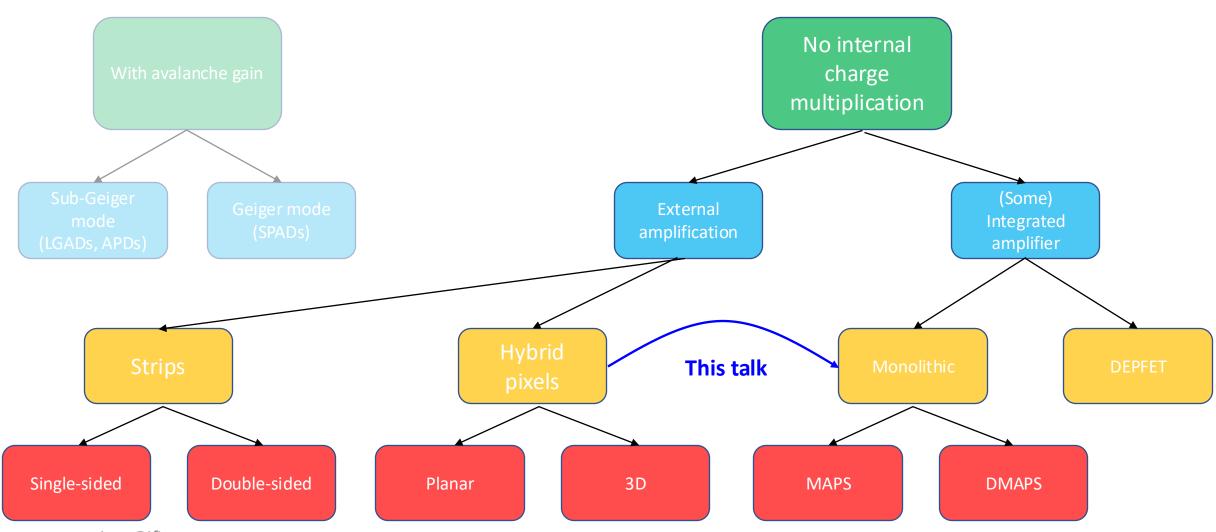

## Semiconductor Detector Types

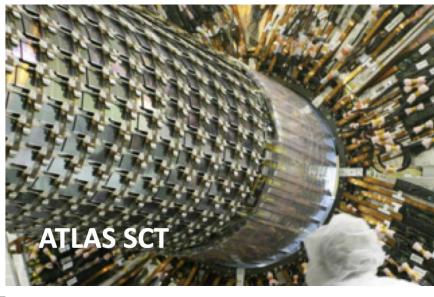

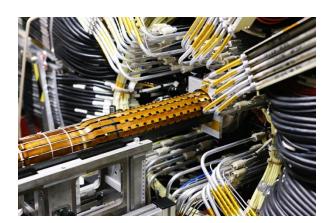

### State-of-the-art of LHC Detectors

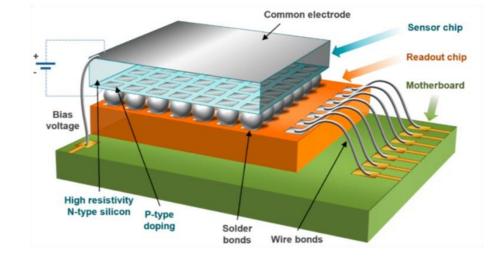

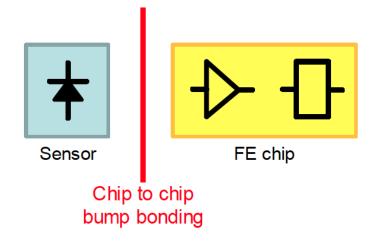

#### All based on **Hybrid Pixel Detectors**

**ATLAS IBL**

LHCb Velo

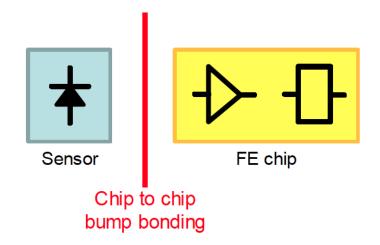

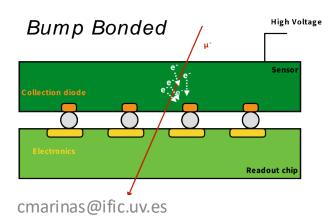

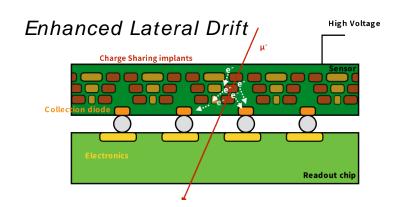

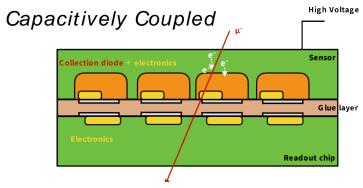

## From Hybrid Pixels to Monolithic

- Standard HYBRID pixels

- Various sensors: planar-Si, 3D-Si, diamond

- Mixed signal R/O chip

### From Hybrid Pixels to Monolithic

- Standard HYBRID pixels

- Various sensors: planar-Si, 3D-Si, diamond

- Mixed signal R/O chip

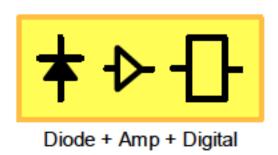

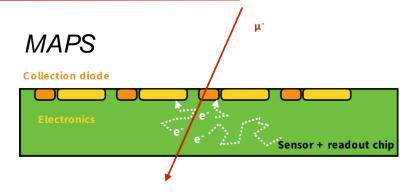

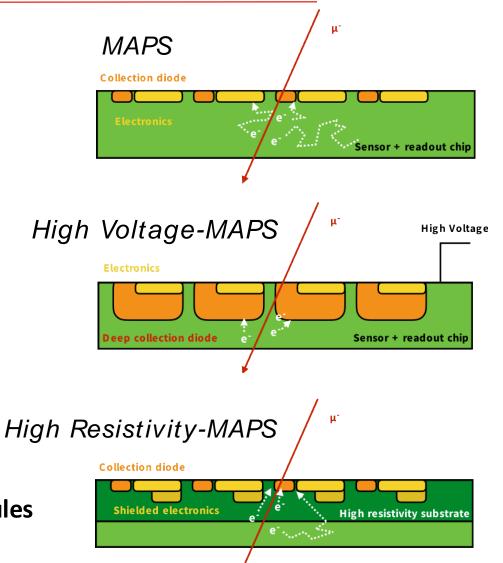

- Monolithic Active Pixel Sensors

- MAPS using CMOS with Q-collection in epilayer (usually by <u>diffusion</u>)

- Depleted DMAPS using HR substrate and/or

HV process to create depletion region

### From Hybrid Pixels to Monolithic

- Standard HYBRID pixels

- Various sensors: planar-Si, 3D-Si, diamond

- Mixed signal R/O chip

- Monolithic Active Pixel Sensors

- MAPS using CMOS with Q-collection in epilayer (usually by <u>diffusion</u>)

- Depleted DMAPS using HR substrate and/or

HV process to create depletion region

Moderate spatial resolution (10-100  $\mu$ m) High material budget (few %  $X_0$ ) High cost Radiation hard

High spatial resolution (1  $\mu$ m) Low material budget (0.1 %  $X_0$ ) Needs modifications for radiation Simpler readout architecture

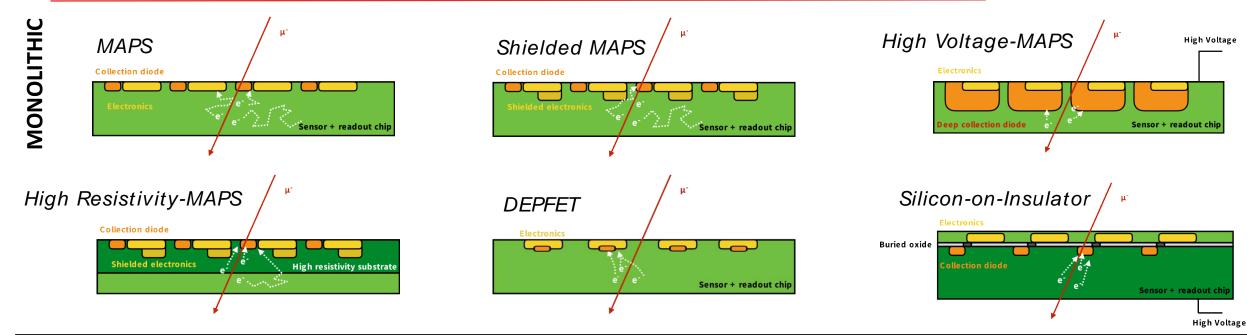

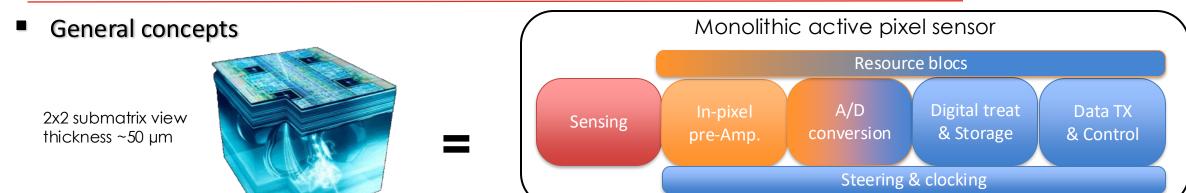

### (D)MAPS

#### (Depleted) Monolithic Active Pixel Sensors

#### Monolithic

Signal generation + readout integrated on a single unit Low material budget

#### Active

Detection and in-pixel amplification and processing

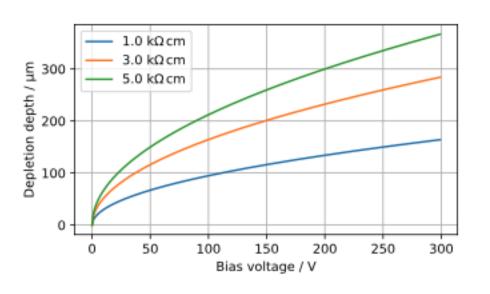

#### Depleted

HV process or HR substrate to create depletion region Fast charge collection via drift Large depleted volume with large signal

$$d \sim \sqrt{\rho \cdot V}$$

## (D)MAPS

#### (Depleted) Monolithic Active Pixel Sensors

#### Monolithic

Signal generation + readout integrated on a single unit Low material budget

#### Active

Detection and in-pixel amplification and processing

#### Depleted

HV process or HR substrate to create depletion region Fast charge collection via drift Large depleted volume with large signal

$$d \sim \sqrt{\rho \cdot V}$$

Very low mass, small pixel sizes, highly integrated modules

## Many Different Implementations

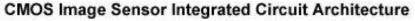

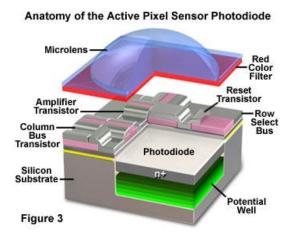

## CMOS Image Sensors (CIS)

- All-in-one: Electronic Camera On Chip

- Standard CMOS technology:

- > Lower production costs

- ➤ Simpler integration of complex functionalities

- Very small pixels (1 um, 40 M pixels)

- Single low supply and power consumption

- Increased speed (column- or pixel parallel processing)

## CMOS Image Sensors (CIS)

- All-in-one: Electronic Camera On Chip

- Standard CMOS technology:

- > Lower production costs

- ➤ Simpler integration of complex functionalities

- Very small pixels (1 um, 40 M pixels)

- Single low supply and power consumption

- Increased speed (column- or pixel parallel processing)

### **Commercial Vendors**

Various processes in use currently in HEP:

TowerJazz 180 nm, 65 nm

TSI 180 nm

L-Foundry 150, 110 nm

Globalfoundries 130 nm ...

Monolithic sensor technologies based on commercial processes

Reduced cost, large throughput, fast turnaround, large wafers

Complex layouts, limited information on processing details, long term support

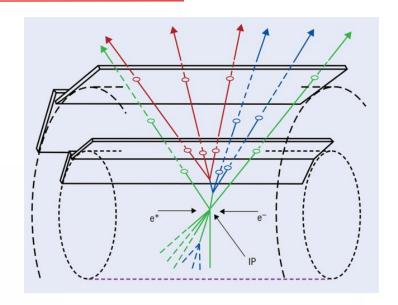

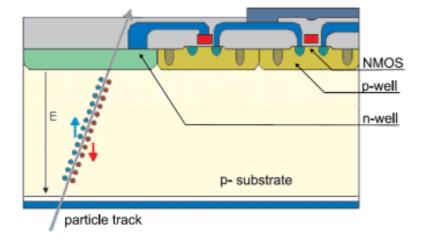

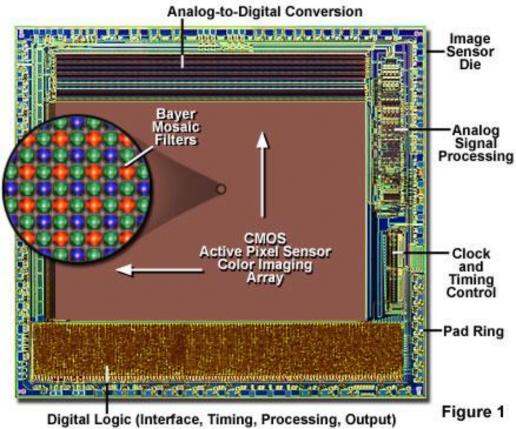

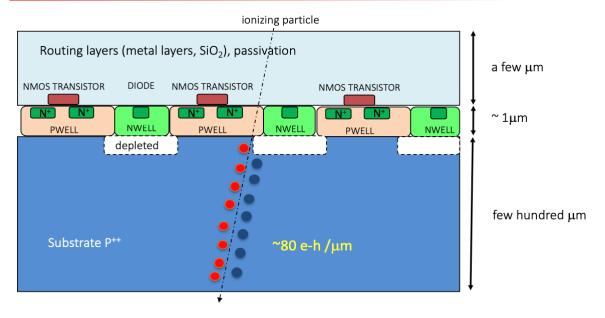

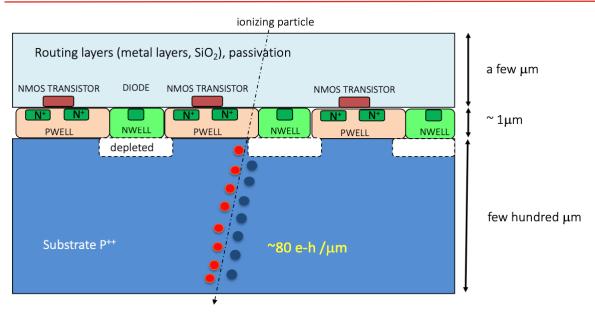

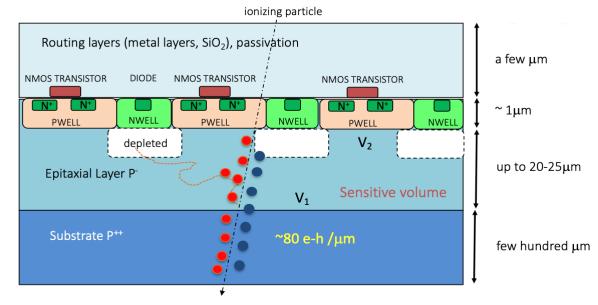

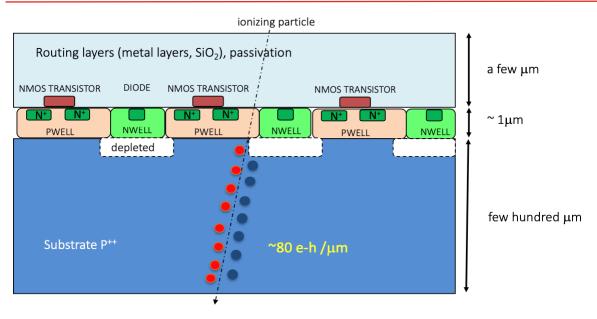

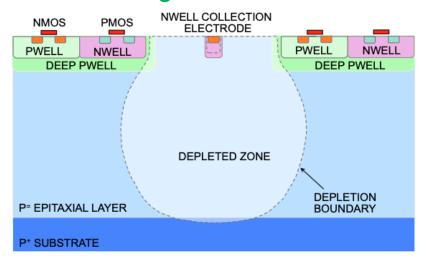

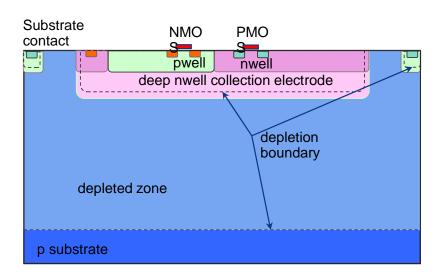

### Particle Detection in CMOS APS

In standard CMOS image sensors, the photodiode is implanted in low-resistivity silicon.

Depletion is shallow

Charge collection efficiency is low

The detector element covers a small fraction of the pixel area

-> Not suitable for measurement of charged particles

### Particle Detection in CMOS APS

In standard CMOS image sensors, the photodiode is implanted in low-resistivity silicon.

Depletion is shallow Charge collection efficiency is low The detector element covers a small fraction of the pixel area

-> Not suitable for measurement of charged particles

Use of an epitaxial layer with doping few orders of magnitude smaller than the one on the p++ substrate

Potential barriers at boundaries:

$$V_1 = rac{kT}{q} ln rac{N_{sub}}{N_{epi}}$$

$V_2 = rac{kT}{q} ln rac{N_{PWELL}}{N_{epi}}$

Which keep minority carriers confined in the epi-layer until they reach the depleted region under nwell 22

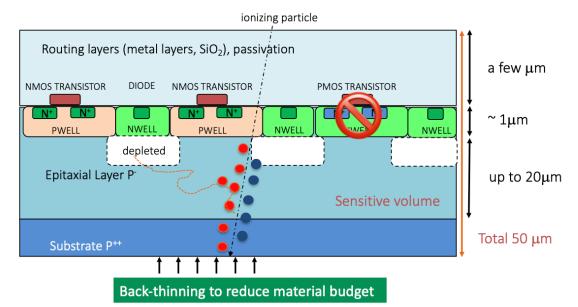

## Particle Detection in (Thinned) CMOS APS

In standard CMOS image sensors, the photodiode is implanted in low-resistivity silicon.

Depletion is shallow Charge collection efficiency is low The detector element covers a small fraction of the pixel area

-> Not suitable for measurement of charged particles

Use of an epitaxial layer with doping few orders of magnitude smaller than the one on the p++ substrate

Potential barriers at boundaries:

$$V_1 = rac{kT}{q} ln rac{N_{sub}}{N_{epi}}$$

$V_2 = rac{kT}{q} ln rac{N_{PWELL}}{N_{epi}}$

Which keep minority carriers confined in the epi-layer until they reach the depleted region under nwell

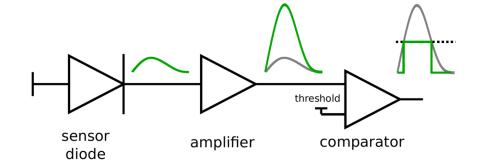

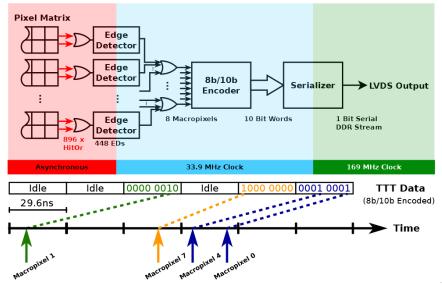

### Readout Architectures

Generalities

Assume digitisation

Need to absorb the max hit rate

Power connected to clock-speed

- Multiplexing toward output (! bottleneck)

- Potential trigger logic

- Power depends on memory management

- Power depends on read-out rate (#outputs and clock)

- Synchronous

- Priority encoder: ALPIDE, MIMOSIS

=> adapted for stitching: MOSS

- Column-drain architecture: MONOPIX

- Data driven, fired pixel adress within 20 ns over 2cm

- Asynchronous

- no in-matrix clock → lower power

- Still data-driven

- MALTA with pulses through

- Adapted to stitching: MOST

- Complex logic

- MIMOSIS case

- Required by fluctuating rate

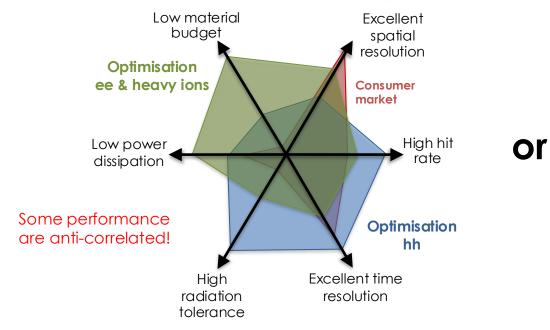

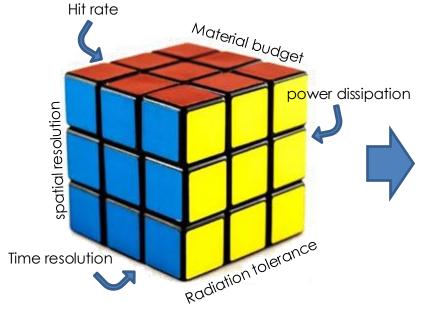

### CMOS-MAPS R&D in a Nutshell

R&D topics for each box

Performance is a matter of optimisation

### **Towards Better Radiation Tolerance - I**

#### Electrode design

Electronics outside the charge collection well

#### Small collection electrode

Very small sensor capacitance (<5fF)

→ Low noise, low power, high speed

Longer drift distances and low field regions

→ Radiation hardness needs improvements

Electronics inside the charge collection well

#### Large collection electrode

No low field regions

Shorter drift distances

Less trapping → More radiation hard

Larger sensor/well-well capacitance (>100 fF)

→ Penalties in noise/power/speed

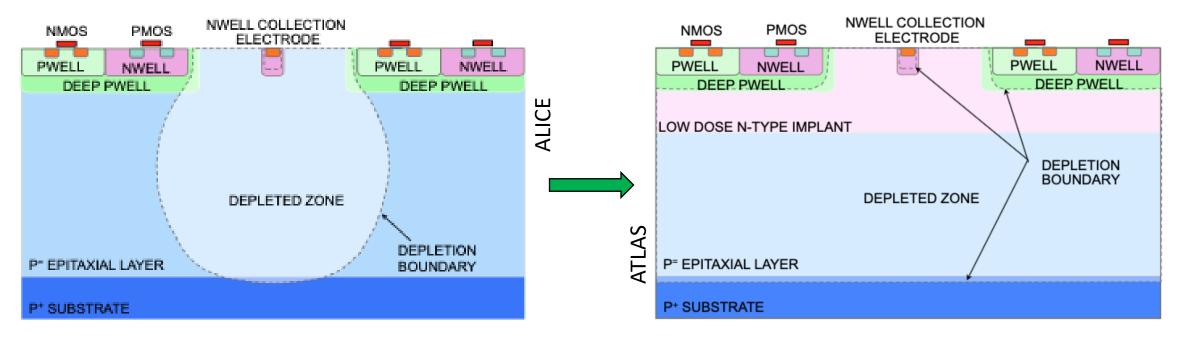

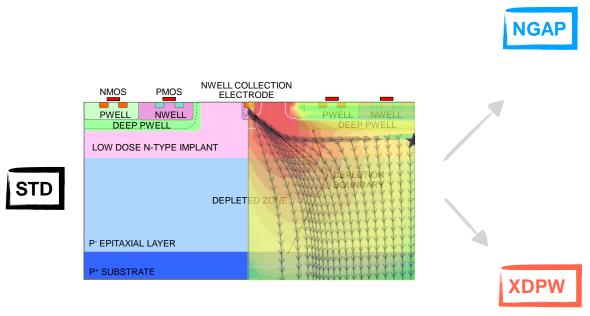

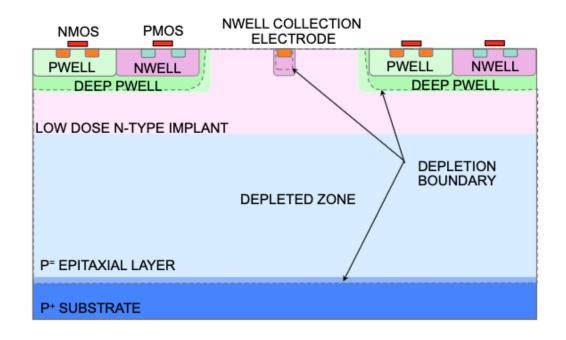

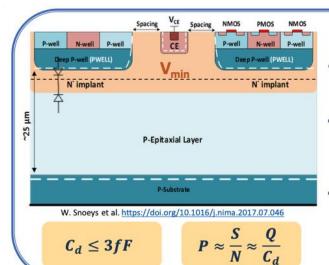

### Towards Better Radiation Tolerance - II

#### Process modification

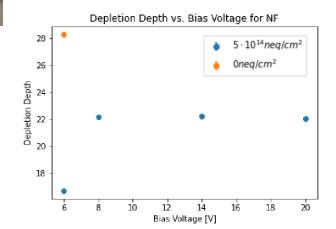

• Partially depleted epitaxial layer Charge collection time < 30 ns Operational up to  $10^{14} \text{ 1 MeV } n_{eq}/\text{cm}^2$

- Modified process: Additional planar n-type implant Full depleted epi layer (up to 40 um deep)

Fast charge collection < 1 ns</li>

- 3 nm gate oxide for good TID

- → Order of magnitude improvement in rad. hardness

## TJ-Monopix Pixel Design Issues

28

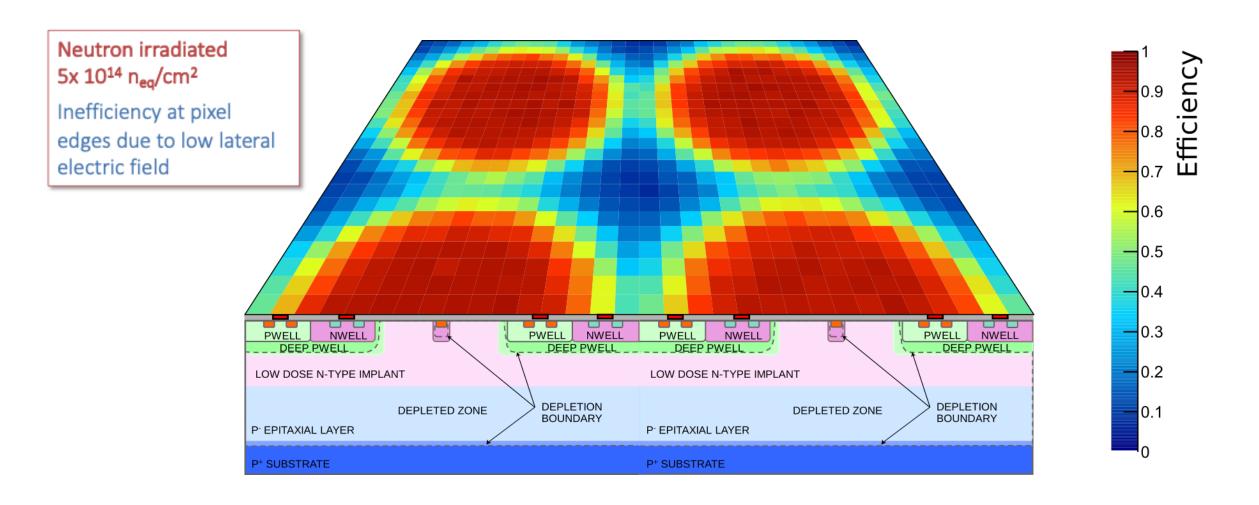

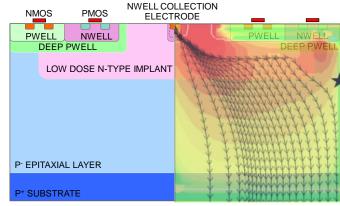

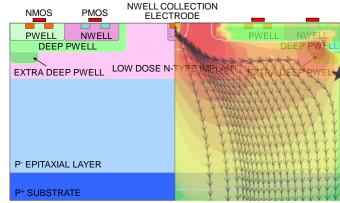

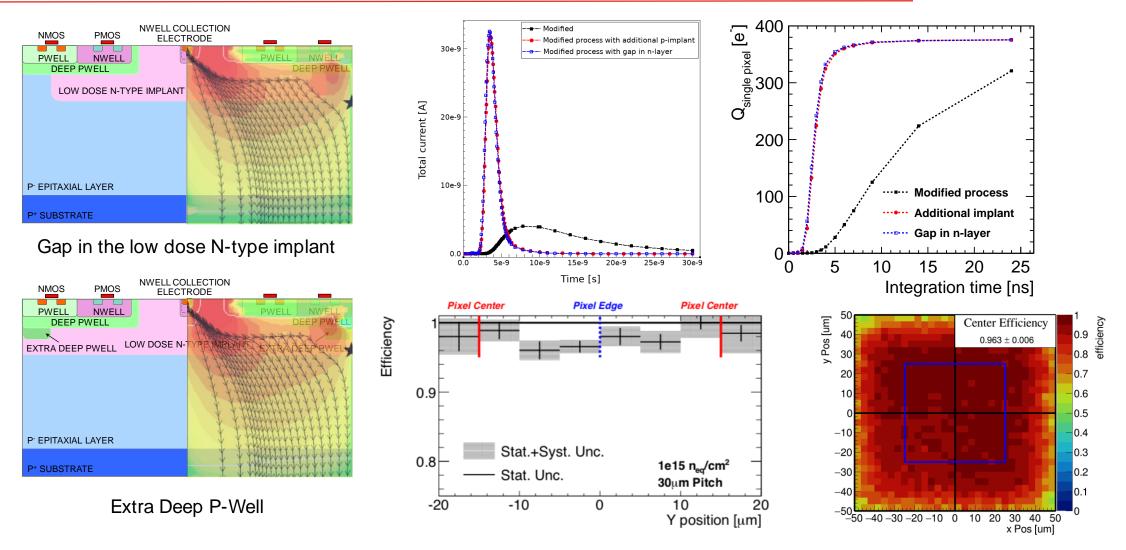

## TJ-Monopix/MALTA Modifications

#### Gap in the low dose N-type implant

Extra Deep P-Well

#### Goal:

- Bend the field lines towards the collection electrode

- Shorten the drift path

- Increase charge collection speed, specially at pixel borders

## TJ-Monopix/MALTA Modifications

→ Result: Faster charge collection, larger signal, high efficiency

### Conclusions

• CMOS vertex and trackers in HEP are a mainstream technology:

Construction of large trackers for LHC

Possibilities for future upgrades (Belle II, LHCb, NA64) and new machines (Higgs factories)

Strong interest for R&D to fully exploit potential of DMAPS

High granularity

Low material budget

Large area (vertexing, tracking, calorimetry, TOF) at reduced cost

Utilize industry postprocessing

Build compact, highly integrated modules

- Semiconductor trackers, and CMOS in particular, are here to stay...

- The devil is in the details

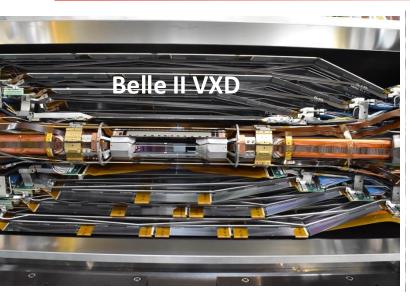

# The Belle II VXD Upgrade

C. Marinas

IFIC – Valencia

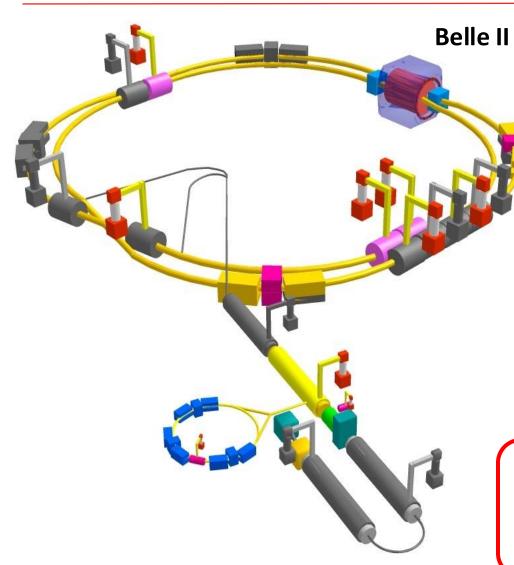

### SuperKEKB and the Belle II Experiment

- SuperKEKB: Asymmetric energy  $e^+e^-$  collider  $E_{cm} = m(\Upsilon(4S)) = 10.58 \text{ GeV}$

- Peak luminosity:  $\mathcal{L} = 6.10^{35}$  cm<sup>-2</sup> s<sup>-1</sup> (x30 than KEKB) Beam size reduction. Higher current (x2 higher).

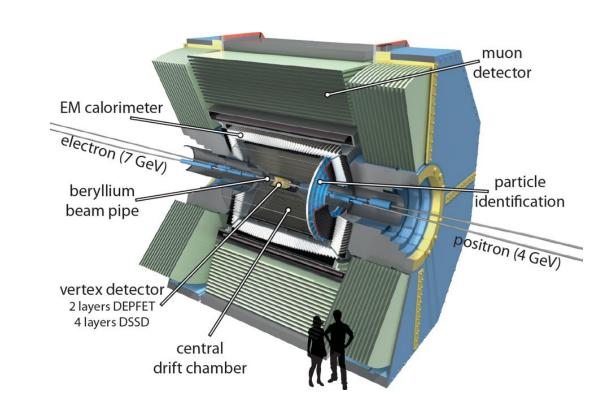

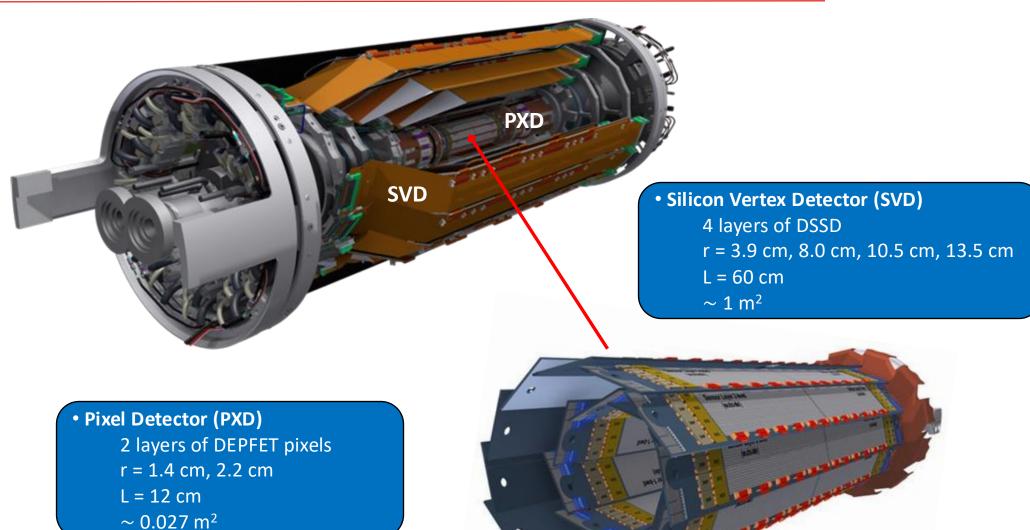

### Belle II Vertex Detector

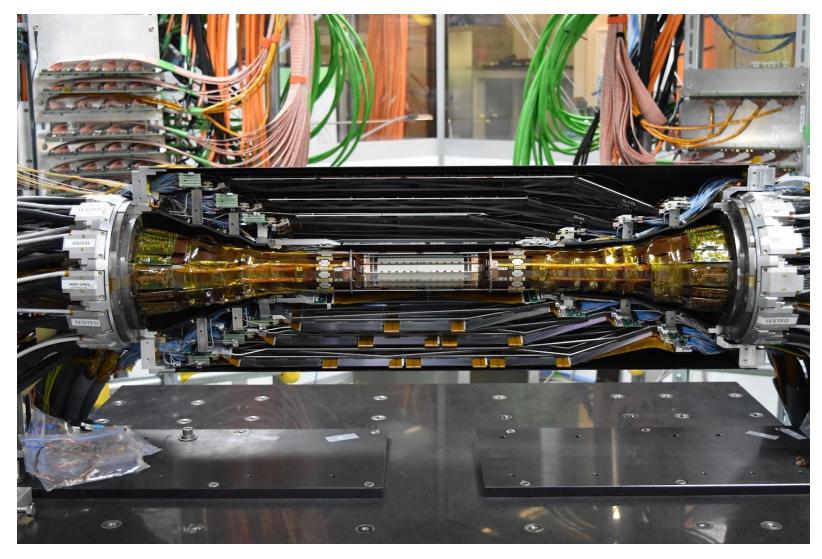

## Belle II VXD

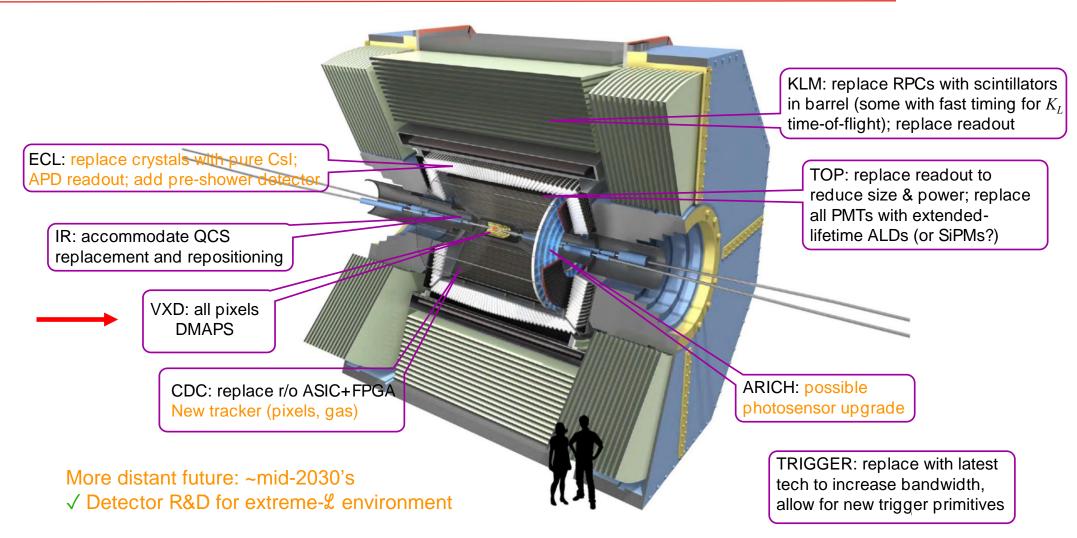

## Belle II Upgrades

# Requirements for VXD Upgrade

### Upgrade motivation:

- Cope with larger background activity

- Improve momentum and impact parameter resolution in low p<sub>T</sub> region

- Simplify tracking chain with all layers involved

- Operation without special modes nor data reduction

### **Key sensor specifications:**

- Pixel pitch 30-40 μm

- Integration time ≤100 ns

- Power dissipation  $\leq 200 \text{ mW/cm}^2$

### Improve physics reach per ab<sup>-1</sup>

| Radius range                                                    | 14 – 135 mm                                   |  |

|-----------------------------------------------------------------|-----------------------------------------------|--|

| Tracking & Vertexing performance                                |                                               |  |

| Single point resolution                                         | < 15 μm                                       |  |

| Material budget                                                 | $0.2\% X_0 / 0.7\% X_0$ inner- / outer- layer |  |

| Robustness against high radiation environment (innermost layer) |                                               |  |

| Hit rate                                                        | ~ 120 MHz/cm <sup>2</sup>                     |  |

| Total ionizing dose                                             | ~ 10 Mrad/year                                |  |

| NIEL fluence                                                    | ~ 5e13 n <sub>eq</sub> /cm²/year              |  |

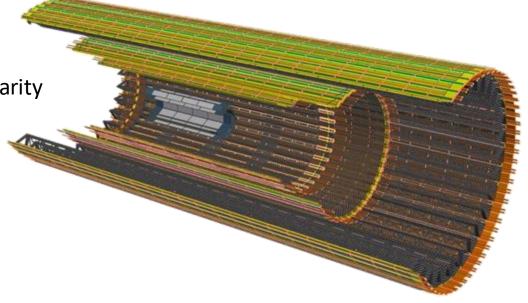

# Belle II Upgrade: VTX - DMAPS

- 5 straight layers barrel, using CMOS pixel sensors

- Low material :  $0.2\% X_0 (L1+L2) 0.5\% (L3) 0.8\% X_0 (L4+L5)$

- Moderate pixel pitch ~ 30 μm²

- Time precision 50-100 ns

- Option for track-triggering with a fast low-space-granularity

- iVTX: innermost 2 layers, self-supported, air cooled

- oVTX: 3 outer layers, CF structure, water cooled

- Overall service reduction and operation simplification

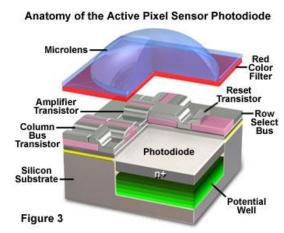

# Small Electrode Sensor Design DMAPS

39

Monolithic detector: Combine sensor and readout on the same wafer

Electronics outside the collection well Small fill factor

- Very small sensor capacitance

- Low noise and power

TowerJazz 180 nm CIS

- Deep pwell allows for full CMOS in pixel

- High resistivity epi-layer 1-8 kOhm.cm

Epi thickness 18-40 μm

- 3 nm gate oxide for good TID

- Modified process: Additional planar n-type implant Full depleted volume

Fast charge collection

- Derived from LHC developments

# **TJ-Monopix Family**

### DMAPS in TJ 180 nm: Concept

- Small sensor capacitance (Cd)

- · Key for low power/low noise

- Radiation tolerance challenges

- **Modified process**

- Small pixel size

- Design challenges

- Compact, low power FE

- Compact, efficient R/O

### Large scale demonstrator chip development

- MALTA

- · Asynchronous readout

- TJ-Monopix1

- Synchronous column-drain R/O

- Process modification enhancements, Cz substrate ⇒ improved efficiency

- TJ-Monopix2: Improved full-scale DMAPS

**Present**

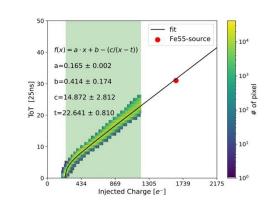

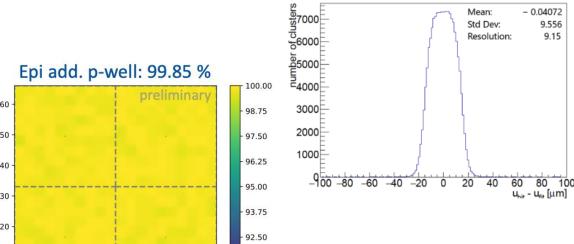

# TJ-Monopix2 Characterization

- TJ-Monopix2 as forerunner of OBELIX

- 33x33 μm<sup>2</sup> pitch, 25 ns integration, 2x2 cm<sup>2</sup> matrix

- 7 bit ToT information, 3 bit in-pixel threshold tuning

- Various sensing volume thickness (CZ-bulk, epi-30 μm)

- In-laboratory

- Threshold / noise

- ToT calibration

- In-beam (DESY, 5 GeV electrons)

- Efficiency ~99%

- Position resolution ~9 μm

10

column [um]

91.25

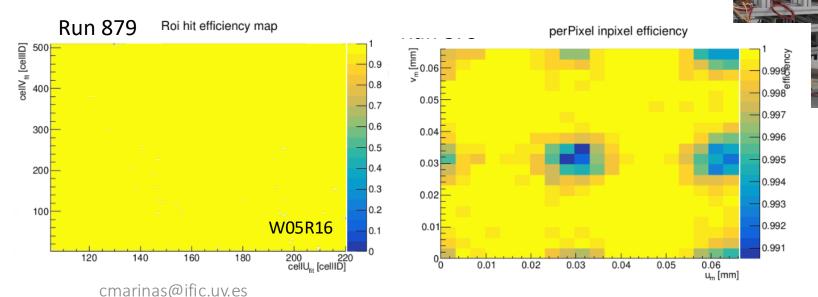

# Irradiated TJ-Monopix2 Test Beam

| Serial | Irradiation    | Substrate |

|--------|----------------|-----------|

| W02R05 | None           | 30 μm EPI |

| W02R09 | Neutrons 1 × 🕮 | 30 μm EPI |

| W05R16 | Protons 5 × 🕮  | 30 μm EPI |

| W08R19 | None           | 30 μm EPI |

| W14R12 | None           | Cz        |

Parameter scans:

HV, IBias, PSub, VClip, BCID, ...

Angular scans, resolution, efficiency

Efficiency >99% for  $5x10^{14}$   $n_{eq}/cm^2$  (310  $e^-$  threshold) Cluster position residuals ~9.5  $\mu m$

Telescope Telescope planes 4-6 planes 1-3

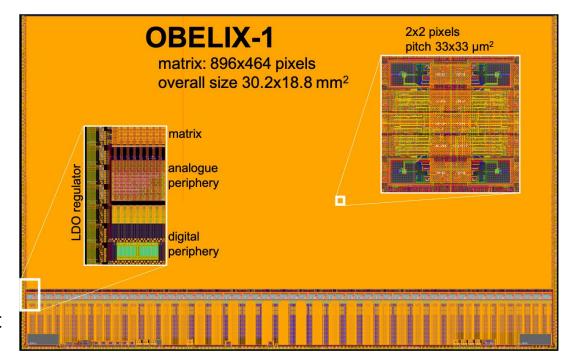

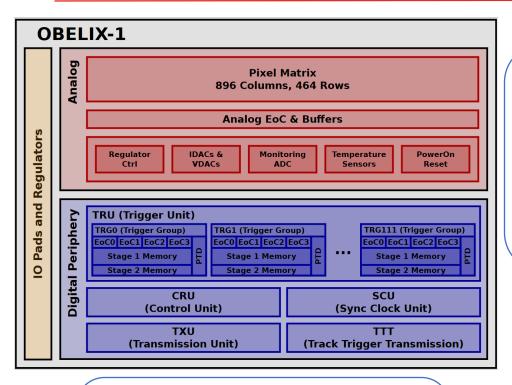

# **OBELIX** Design

- Matrix design

- Extended copy of TJ-Monopix2

- 2 front-end flavours: DC- and AC- cascode amplifier

- Clock for time-binning slowed down: 100ns

- Powering

- LDO regulator for easier voltage distribution

- Overall power depends on hit rate: 200-300 mW/cm<sup>2</sup>

- Trigger Unit

- Simulated with realistic inputs: 120 MHz/cm<sup>2</sup>

- Can sustain 600 MHz/cm<sup>2</sup> for 0.5 μs

- Fine time stamping

- 6 ns achievable with end-of-column fast clock

- Limited to hit rate ≤ 10 MHz/cm<sup>2</sup>

- Track trigger

- Reduced granularity to 8 strixels (~4 x18 mm²)

- Increased transmission rate: 33 MHz

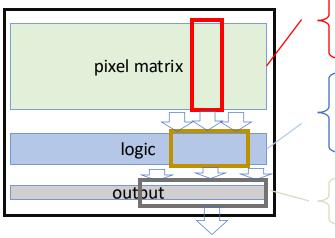

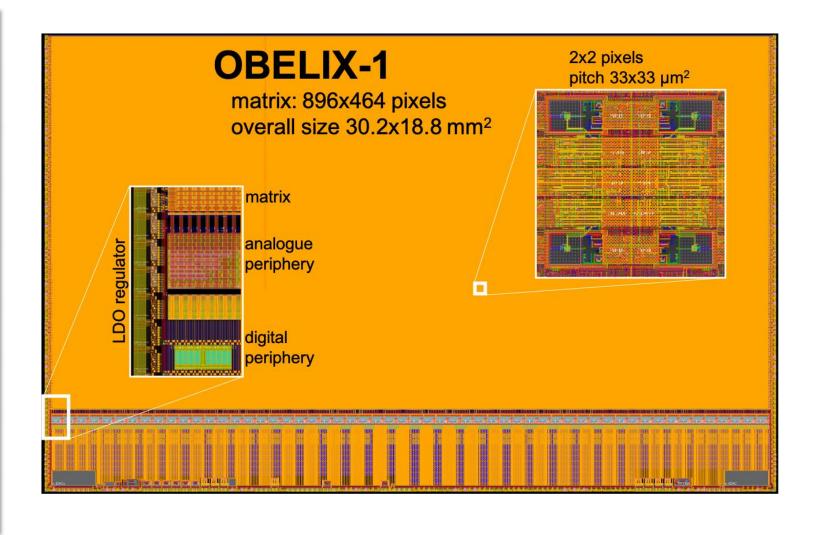

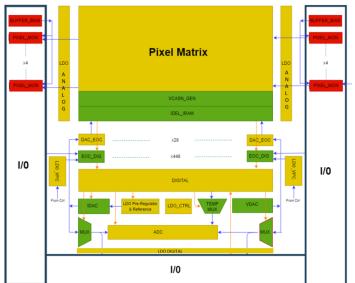

# **OBELIX Layout**

| Pitch                      | 33 µm                                   |

|----------------------------|-----------------------------------------|

| Signal ToT                 | 7 bits                                  |

| Integration time           | 50 To 100 ns                            |

| Time stamping              | ~5 ns<br>for hit rate < 10 MHz/cm²      |

| Hit rate max for 100% eff. | 120 MHz/cm <sup>2</sup>                 |

| Trigger handling           | 30 KHz<br>with 10 µs delay              |

| Trigger output             | ~30 ns resolution with low granularity  |

| Power<br>(with hit rate)   | 120 to 200 mW/cm²<br>(1 to 120 MHz/cm2) |

| Bandwidth                  | 1 output 320 MHz                        |

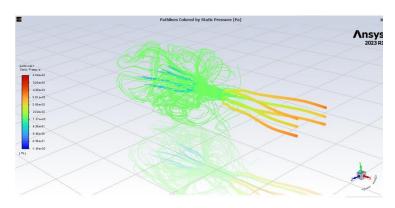

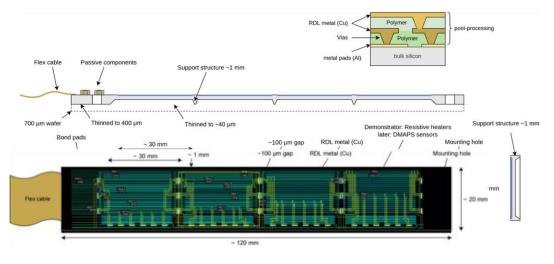

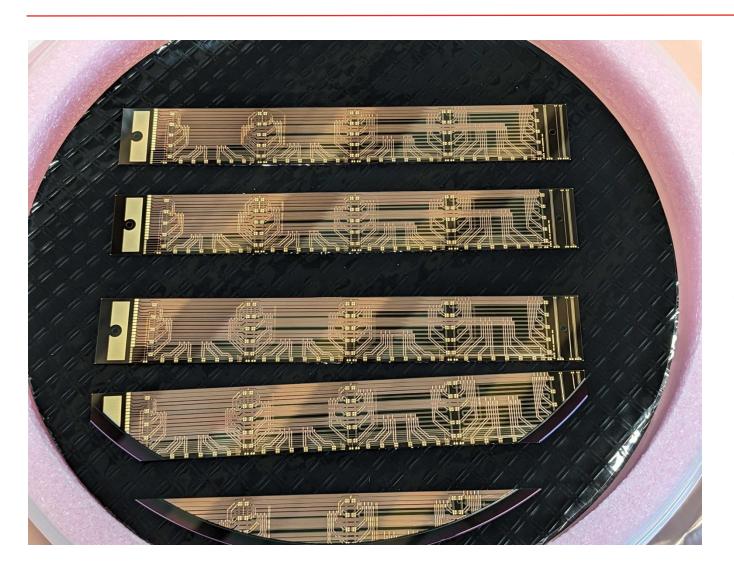

# iVTX Inner Layer Concept

- All-silicon module < 0.15 % X<sub>0</sub>

- 4 contiguous sensors diced as a block from the wafer

- Redistribution layer for interconnection

- Heterogeneous thinning for thinness & stiffness

- Prototyping

- First real-size ladders at IZM-Berlin with dummy Si

- True iVTX geometry available

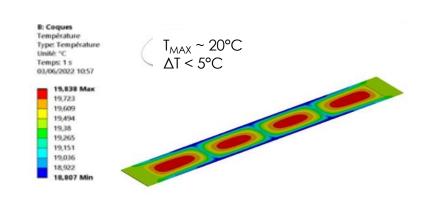

- Simulation on cooling

- Dry air cooling 15°C

- Assume 200 mW/cm<sup>2</sup>

### iVTX Ladder Demonstrator

Production finished smoothly:

FE-I3 and heaters 300 – 700 um thick

Characterization started:

First quality inspection with needles shows resistivity is on the expected range.

Integrity of data lanes will follow

# Summary: Belle II VXD Upgrade Plans

- *Vertex detector*: Plans to replace VXD with a fully pixelated CMOS detector (VTX)

- TJ-Monopix2 performance, including irradiated devices, matches expectations

→ Solid steppingstone towards OBELIX, to be submitted in 2025

- Complete ladder demonstrators available, including its test stands

- Preparing the next big step: TDR

# **THANK YOU**

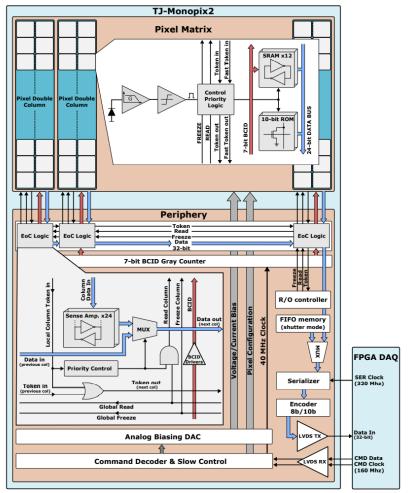

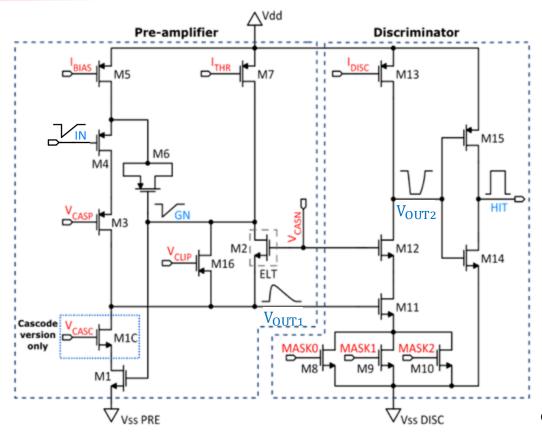

# TJ-Monopix2 as Prototype

Active Matrix Area: 512 × 512 pixels

Normal FE

Cascode FE

HV FE

Casc.

HV FE

Casc.

HV FE

Digital End of Column (SenseAmp, drivers & buffers)

Digital Chip Bottom

I/O and Periphery Power Pads

Layout of TJMP2 sensor: divided in 4 regions with different FE

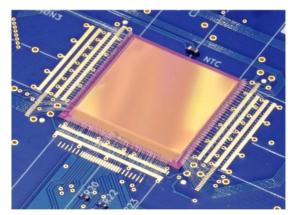

TJM2 sensor bonded on a test board

- Developed for ATLAS experiment

- FE derived from ALPIDE

- 4 FE flavors with differences in the amplifier and detector input coupling (AC or DC)

- Column-drain R/O architecture

- DMAPS Tower Semiconductor 180 nm CMOS

- $2 \times 2 \text{ cm}^2 \text{ chip: } 512 \times 512 \text{ pixels}$

- Pixel pitch: 33.04×33.04 μm²

- Expected from design (simulations):

- $\circ$  ~ 100 e- min threshold

- 5-10 e- threshold dispersion (tuned)

- $\circ$  >97% efficiency at  $10^{15} n_{eq}/\text{cm}^2$

- $\sim$  5 e- noise

- Fully efficient with hit rate 120 MHz/cm²

- $\circ$  Power:  $\sim 1 \,\mu\text{W/pixel}$

**Base-line option for OBELIX design**

Chip architecture of TJMP2

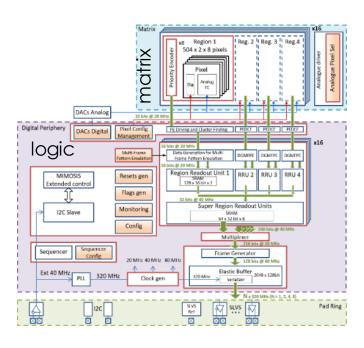

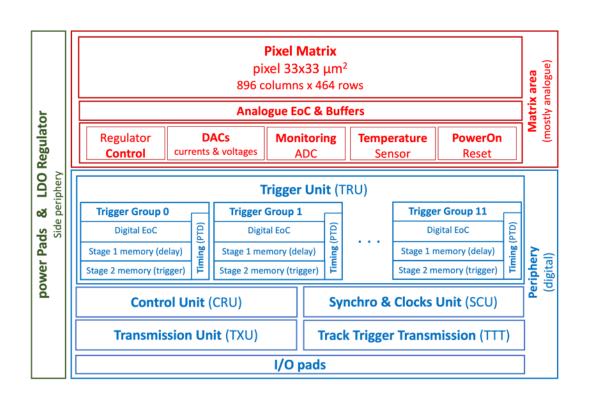

# **OBELIX Block Diagram**

### **Digital Periphery**

- o Main clk-in: 170MHz

- New end-of-column adapted to Belle II trigger

- Timestamped hits stored in memories

- Read-out when timestamp matched with trigger

- Single output at 340 MHz average bandwidth

- RD53 control/readout protocol

### **Power pads**

- Power regulators

- Simplified system integration

### Analog

- Pixel matrix adapted from TJMP2

- Column drain architecture

- Monitoring ADC

- Temperature sensors

- Based on current characterisation and simulation results, 2 FE flavors are chosen for OBELIX on equal area:

- Cascode FE (DC)

- HV Cascode FE (AC)

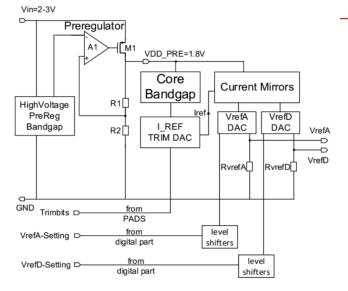

# **OBELIX Power Management**

- Power distribution is a major concern as OBELIX is larger than TJMP2, leading to performance degradation

- Long linear ladders voltage drop across ladder

- On chip regulators are developed to compensate the voltage drop and simplify the power distribution

- Two analog LDO (Low Dropout) regulators to supply the matrix from both sides

- A digital LDO in the bottom of the chip to supply the digital blocs

- A preregulator to supply LDO references generator

- A VPC (Voltage pre-charge) LDO to reset and recharge bit-lines between each read cycle

- The LDO generates the output voltage of 1.8 V (+ 10%, -20%) necessary for the technology to power the chip

- Wide input supply voltage range of 2-3 V

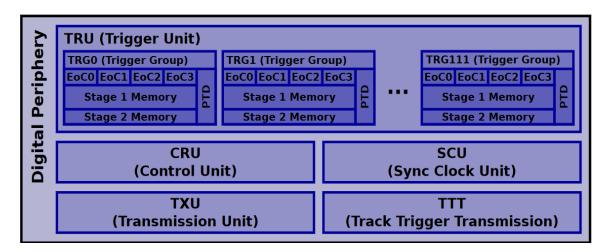

# **OBELIX Digital Periphery**

- Module division: 5 main parts with new modules related to the Belle II trigger

- TRU Trigger Unit: Manage pixel data from the matrix-EOC and wait for the trigger to pick them for output

- PTD Periphery Time to Digital : Precision timing feature → 5ns for hit rate < 10 MHz/cm² (enabled via configuration)

- CRU Control Unit: Implement RD53B interface, command decoder and global configuration

- SCU Sync Clock Unit: Synchronize circuit and clk divider,

Rx data SIPO synchronization

- TXU Transmission Unit: Generate output data and sequential output, data framing, serializer

- TTT The Track Trigger Transmission: Provide coarse and rapid information to the Belle II trigger system

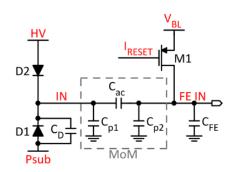

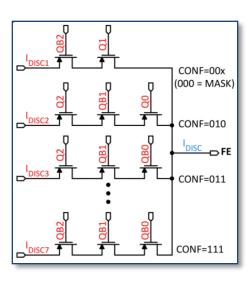

# Analog FrontEnd Design

Pixel Laboratory

- o Two flavors with a cascode pre-amplifier :

- With an input DC-coupling using a forward biased diode (Cascode FE)

- With an input AC-coupling allowing higher bias voltage above 30V (HV Cascode FE)

Input DC-coupling

Input AC-coupling

Individual pixel masking

#### *3-bit Threshold Tuning DAC*

A 3 bit threshold tuning is available at the pixel level to reduce the threshold dispersion

# OBELIX – Layout

- Matrix inherited from TJ-Monopix2 developed for ATLAS (Tower 180 nm CIS)

- Dimensions adjusted to VTX geometry

464 rows and 896 columns, 29.60 x 15.33 mm<sup>2</sup> active area

- Low dropout regulators (LDOs) to allow a wide input supply voltage range 2-3 V

- Clock frequency for the timestamp and trigger unit is 21.2

MHz (timestamp length 47.2 ns)

- Trigger unit with 2-stage trigger memory (data loss < 0.02% at design trigger latency of 10  $\mu$ s and hit rate of 120 MHz/cm<sup>2</sup>

- 320 Mbit/s output