# PACIFIC: ASIC de lectura de SiPM para el Upgrade de LHCb

José Mazorra de Cos

Instituto de Física Corpuscular (CSIC-UV)

EXCELENCIA

SEVERO

OCHOA

# Presentación

- José Mazorra de Cos (Despacho 117).

- Oct '11 - Oct '13: JAE TEC (U. Electrónica).

- Ene '14 - Ene '17: por proyecto (Grupo LHCb).

FIU-IFIC, CPI-13-452 (10 meses)

GVPROMETEOII2014-049 (2<sup>1</sup>/<sub>4</sub> años)

- Feb '17 - Ene '20: PTA (U. Electrónica).

- Dedicación principal: Upgrade LHCb.

- Tareas para la unidad de electrónica:

- Test térmicos de DEPFET (Belle II).

- Diseño: VATAHDR64, DEGAS y DEPFET.

- Reparación: alimentador PMT y lab. dept.

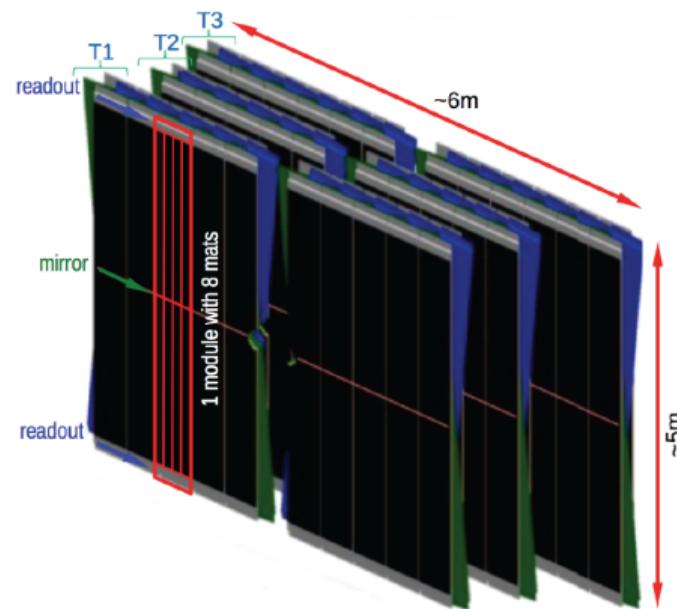

# Scintillating Fibre Tracker

- El SciFi Tracker sustituirá a los detectores de bandas de silicio (strips) y tubos de deriva (straw tubes) del las estaciones de trazas de LHCb en el Upgrade (2019-20).

- Fibras plásticas  $250\mu\text{m}$  con espejo.

- Lectura: arrays de SiPM de paso  $250\mu\text{m}$ .

- Tres estaciones con cuatro planos, dos verticales, dos estereoscópicos ( $\pm 5^\circ$ ).

- Área total  $\sim 340\text{m}^2$  con 590k canales.

- Resolución  $<100\mu\text{m}$  y eficiencia  $>99\%$ .

- Material reducido,  $<1\% X_0$  por plano.

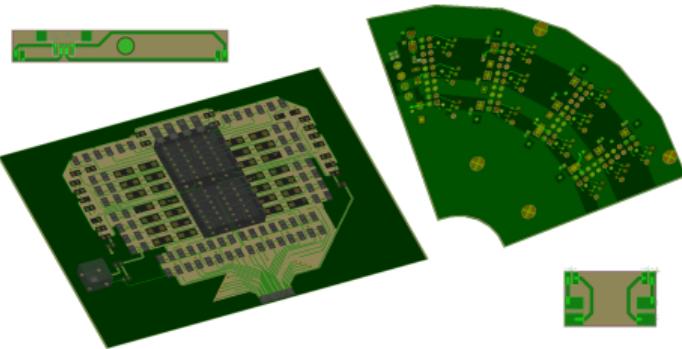

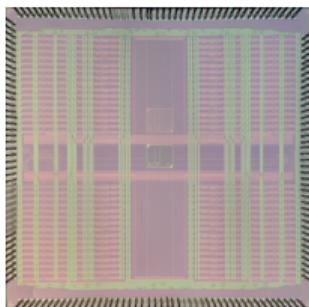

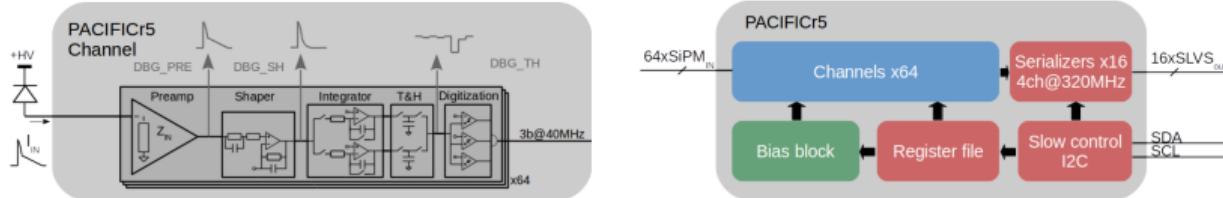

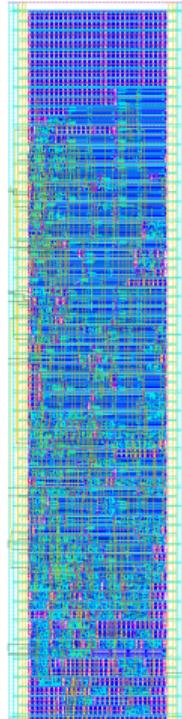

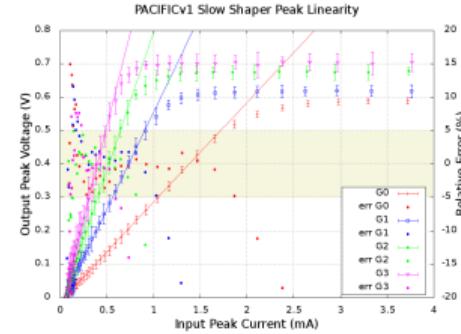

- ASIC de señal mixta con 64 canales diseñado en CMOS 130nm (IBM/TSMC).

- Entrada en baja impedancia permitiendo la conexión directa al sensor.

- Salida digital de 2 bits no lineales, serializando cuatro canales a 320MHz.

PACIFICr5

- Entrada en corriente con control de tensión y gran ancho de banda.

- Filtro de pulsos con doble cancelación polo-zero configurable (10ns).

- Dos integradores intercalados para minimizar tiempo muerto.

- Retroalimentación lenta (filtro) y ajuste de tensión de offset (integrador).

- ADC Flash con tres comparadores de histéresis y umbrales configurables.

- Bloque de referencias controlado desde registros de configuración ( $I^2C$ ).

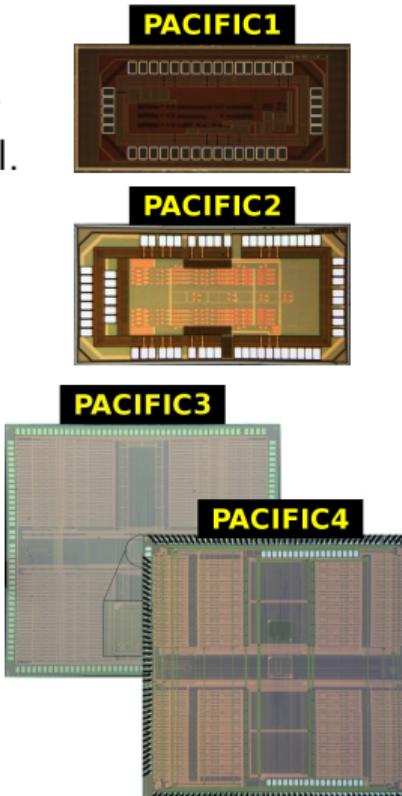

# Versiones

- Chip puramente analógico.

- Canal procesado analógico.

- Canal deconvolución digital.

- Bloques sueltos de test.

- Polarización externa.

- Migración a TSMC.

- Tamaño completo.

- Corrección offset.

- Bloques separados de polarización.

- Ocho canales completos.

- Polarización interna.

- Configuración vía I<sup>2</sup>C.

- Salida analógica por etapa multiplexada por canal.

- Opt. integradores.

- Opt. comparadores.

- Umbrales por canal.

- Mejora en resolución de los umbrales.

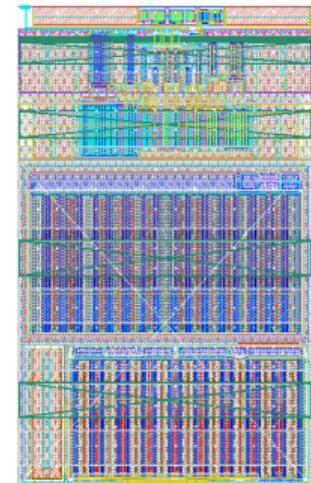

# Diseño Analógico

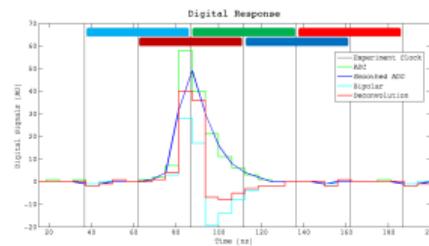

- PACIFICr1: procesado alternativo con deconvolución digital.

- Procesado analógico reducido a preamp y filtro lento, muestreo rápido, deconvolución digital y caracterización.

- Prototipo con salida analógica y procesado digital offline.

- Diseño de un filtro Sallen Key de 2º orden con polos iguales.

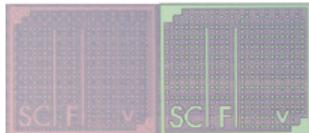

- PACIFICr4: migración de IBM a TSMC (CMOS 130nm).

- Pad digital (TSMC) insuficiente para nuestro sistema de test.

- Diseño de un nuevo pad con corriente de salida aumentada.

(reglas extendidas de diseño para el anillo de pads)

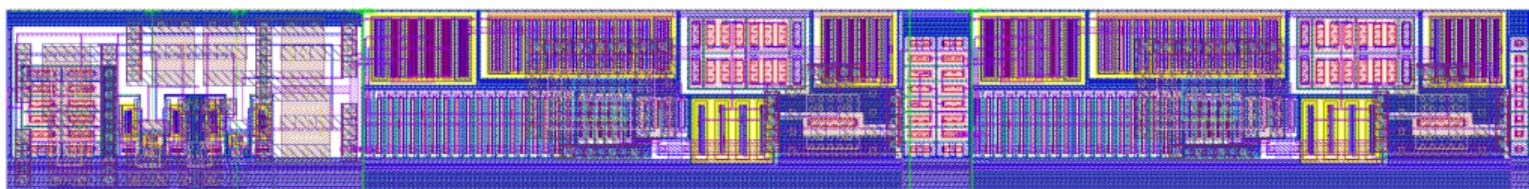

Pad Digital

Filtro lento de conformación de pulso para deconvolución digital

Serializador

- PACIFICr1: deconvolución digital y caracterización de pulsos.

- Estudio de viabilidad con simulaciones en MATLAB.

- Implementación Verilog y estudio del desempeño (NCSim).

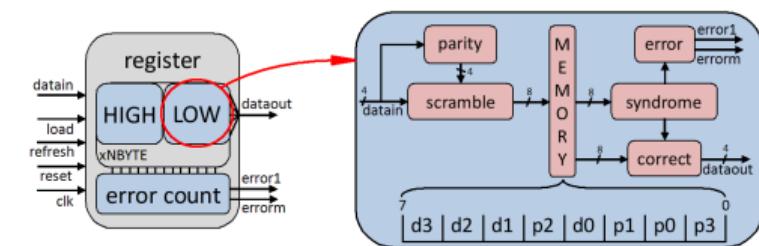

- Diseño del sistema de configuración ( $I^2C$  + registros).

- Direccionamiento a 10b y lectura/escritura multi-byte.

- Registros 8b (opt. área) codificados Hamming(7,4) extendido.

- Registros de sólo lectura (ADC y contador de SEUs).

- PoR (estado inicial) con filtro de protección contra SEUs.

- Adaptación del serializador a cuatro canales (320MHz).

- Verificación de la integración con simulaciones mixtas (AMS).

# Caracterización y Test

- PACIFICr1: sistema de test con salidas analógicas.

- Caracterización del canal de deconvolución digital.

- Sistema de dos PCBs: 1xASIC y 1xFPGA.

- Desarrollo de fw/sw: BER, trim, SEUs ...

- Validación de los bloques digitales.

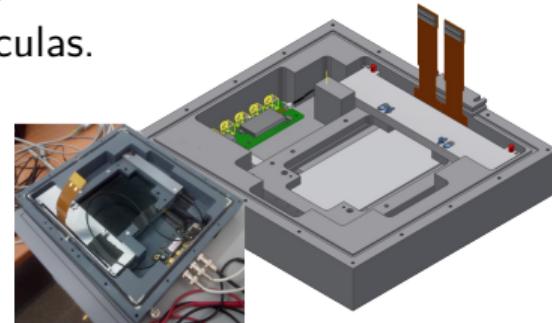

- Diseño de un sistema de test compacto con fibras, SiPM, LED y trigger.

- Permite medidas con luz y partículas.

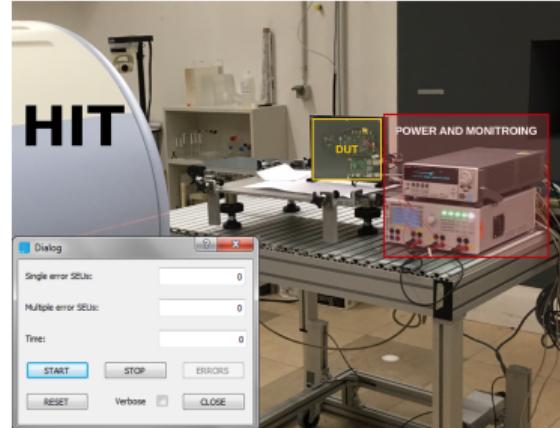

# Test en Instalaciones Radiactivas

- Efectos de radiación en PACIFIC (Feb'17).

- Haz de iones ligeros (HIT, Heidelberg).

- Corriente de fuga (circuito analógico).

- Acumulación de SEUs en los registros.

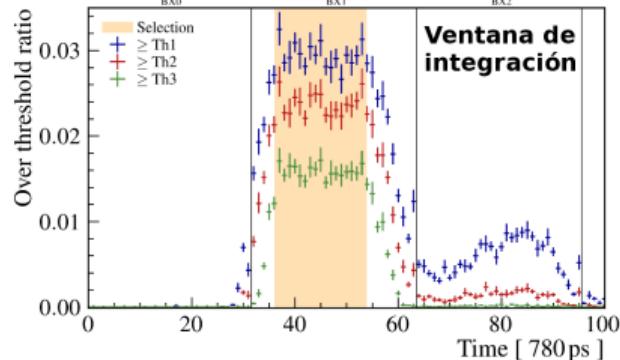

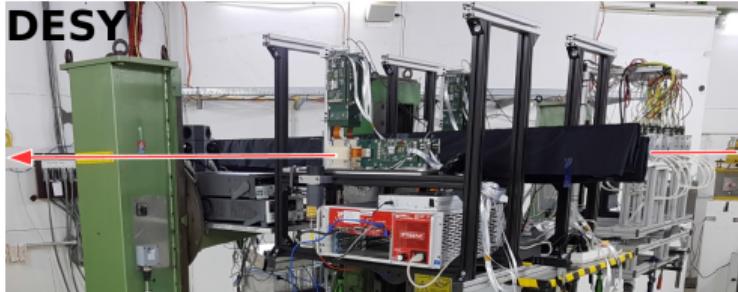

- Test con haz de módulos SciFi (Ago'17).

- Haz de  $e^-$  a 6GeV (DESY, Hamburgo).

- Ventana de integración de PACIFIC.

- Resolución ( $106\mu m$ ) y eficiencia ( $>99\%$ ) limitados por scattering múltiple.

# Perspectivas 2018

- Campaña de estudios de los efectos de radiación sobre PACIFIC.

- Validación del sistema de test en el HIT (Mayo).

- Test con iones pesados en Lovaina (Julio).

- Incluir efectos sobre señales de control asíncronas.

- Campaña de test con haz con sistema completo SciFi en SPS (Julio).

- PACIFIC está en fase de producción desde Enero 2018.

- Se fabrican dos versiones que estarán disponibles en Abril.

- Participación en la caracterización y selección definitiva.

- Test del ~50 % de la producción de las tarjetas portadoras de PACIFIC (Q4).

**Muchas gracias por su atención.**